**SLEC<sup>®</sup> RTL**

Verification Without Testbenches

**SLEC<sup>®</sup> Pro**

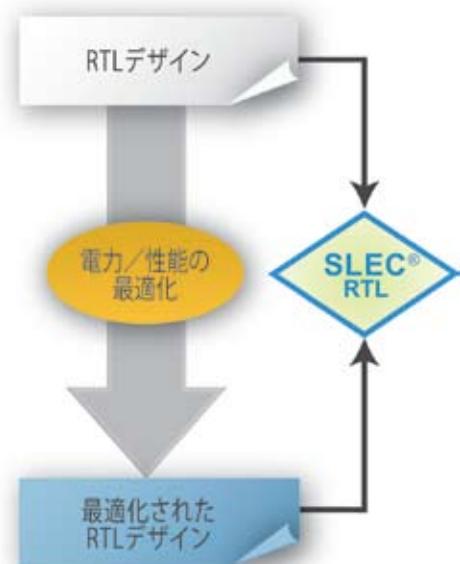

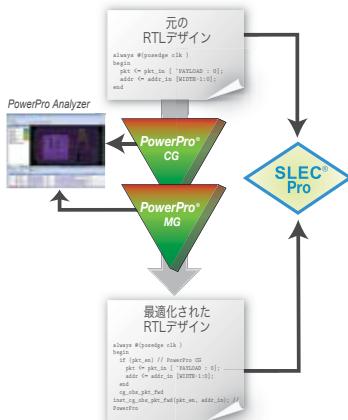

SLEC RTL と SLEC Pro はカリプト社の特許であるシーケンシャル・アナリシス技術に基づいたシーケンシャル・ロジック等価性チェッカー製品です。SLEC RTL は手設計において消費電力、パフォーマンスの最適化を行ったデザインの等価性を検証します。SLEC Pro は PowerPro によって生成された電力最適化の RTL 設計を包括的に検証します。

## RTL 最適化のための機能検証

リタイミング、パイプライン処理、およびクロック・ゲーティングなどの多くの RTL 最適化は設計のシーケンシャルな変更をもたらします。シーケンシャルな変更は内部の信号とポートの動作を変更する可能性があり、テストベンチを変更する必要性を生じ、組み合わせ論理の等価性チェッカーを使うことができなくなります。

SLEC RTL はシーケンシャル・ロジック等価性チェッカーで、最適化された RTL 設計の機能をそれに対応する元の RTL 設計に対してすべての可能な入力について、すべての時間に渡ってフォーマル手法により比較します。SLEC RTL は設計間のレジスタの 1 対 1 のマッピングを必要としないため、シーケンシャルな最適化前後を検証できます。SLEC RTL は、設計者に高性能で低電力設計につながる積極的な設計手法を支援します。SLEC Pro は PowerPro の最適化前後の設計に対して包括的にフォーマル検証を提供します。SLEC Pro と PowerPro のシームレスな統合は検証プロセスを自動化し、RTL 最適化と検証の完全なフローを提供します。

SLEC RTL と SLEC Pro はカリプト社の実証された SLEC 製品ファミリーの一部で、他に SLEC System と SLEC System-HLS もあります。SLEC System は 2 つのシステムレベル・モデル、あるいはシステムレベル・モデルとそれに対応する RTL 設計の機能の等価性を検証します。SLEC System は C/C++、SystemC、VHDL、および Verilog

で書かれた設計をサポートします。SLEC System-HLS は、HLS の生成した RTL を包括的に検証するために、主要な高位合成ツールと共に SLEC System の利点を拡張します。SLEC RTL は SLEC Pro のすべての機能を含んでいます。

## SLEC RTL は他のツールなら見逃す様なバグも発見します

高性能、低電力設計のアプリケーションでは、多くの時間が RTL コードの最適化に費やされ、さらに最適化による機能上のバグを生まなかったことを検証するのに費やされます。これらの最適化手法は手設計において頻繁に起こりうるプロセスです。これらの最適化で生まれた機能上のバグを発見することは、機能上の適用範囲を増やし、発見しにくいバグを検出する為の特別なテストベンチを開発するために、追加の時間を使わない限り、リグレッションのシミュレーションでは出来ないかもしれません。

SLEC RTL は元の RTL と最適化された RTL の間の機能上の等価性が維持されていることを保証することによって、リソース負担の大きいリグレッションを実行する必要性を削減します。

RTL クロック・ゲーティングは設計者によって使用される典型的な電力最適化手法です。しかし、RTL クロック・ゲーティングのイネーブル論理は、シミュレーションベースの検証手法では、制御し、観察することは困難です。一方、SLEC RTL はすべての可能なクロック・ゲーティングのイネーブルおよ

### パワーと性能の最適化の検証

SLEC RTL は手動の RTL 設計最適化の間で起こりうる機能上のバグを発見します。

### 利点

- 設計者に積極的な RTL 最適化を行うための自信を与えます

- シーケンシャルな変更についてのフォーマル等価性チェック

- 長時間を要するリグレッションのシミュレーションを削減します

- 検出が困難な機能上のエラーを検出します

- 短く、簡潔な波形データのトレースでバグを素早く取り除きます

- クロック・ゲーティング最適化の為の特別なテストベンチ開発の必要性を排除します

びディスエーブルの状態に対し、入力のすべての組み合わせを検証します。SLEC RTL は階層構造とブロック境界を越える複雑なクロック・ゲーティングのスキームを取り扱います。

## SLEC RTL の特徴

- Tcl インタフェースとバッチ・モード操作

- VCD と FSDB フォーマットで反例を生成

- 業界基準のシミュレータとデバッグ・ツールとの統合

- PowerPro 最適化フローにおける包括的なフォーマル検証

## SLEC Pro は PowerPro 検証を自動化

SLEC Pro は PowerPro 最適化前後の設計に対して包括的フォーマル検証を提供します。

PowerPro はシーケンシャル・クロック・ゲーティングのイネーブル論理の確認と RTL へのイネーブル論理挿入を自動化し、動的電力を大幅に削減します。PowerPro はレジスタの境界を越え回路動作を評価し、シーケンシャル・クロック・ゲーティングのイネーブル条件を確認し、新しいクロック・ゲーティングのイネーブル論理を追加した RTL コードを生成します。PowerPro の最適化した RTL は SLEC Pro で包括的に検証され、機能上の変更が生じなかったことを保証します。

## 自動化されたフォーマル検証フロー

SLEC Pro は PowerPro が最適化した RTL と元 RTL の等価性を検証します。SLEC Pro 検証は PowerPro によって生成されたセットアップ・スクリプトを用いて自動化されます。

PowerPro はフォーマル検証フローを自動化するための SLEC Pro 起動用のセットアップ・スクリプトを生成します。このセットアップ・スクリプトは PowerPro が最適化した RTL

SI EC 7□=毛々=ト

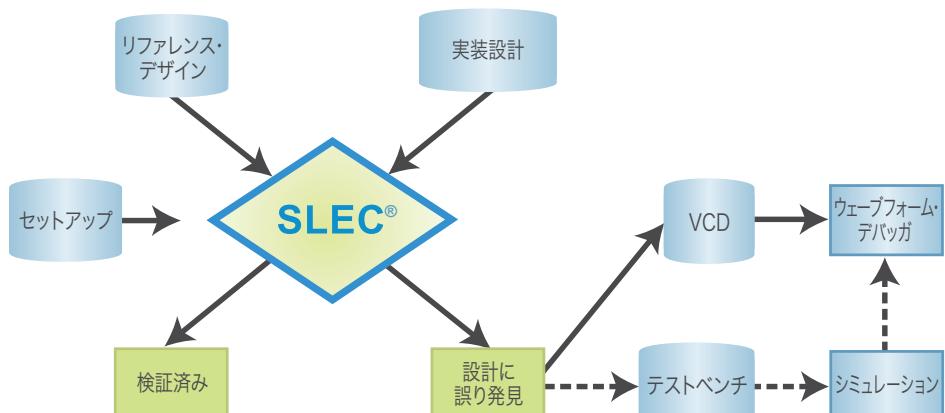

SLEC は元の設計と最適化された設計を読み込みます。Tcl スクリプトは検証シナリオをセットアップし制御します。そして、SLEC は設計が機能上、同一であることを検証するか、またはデバッグのための反例を生成します。反例はデバッグに使用できる波形かシミュレーション・テストベンチです。

と元の RTL が機能上、同一であることを

フォーマルに証明するために必要なすべて

の Tcl コマンドを含んでいます。

## 直感的なユーザインターフェース

SLECによる検証の為のセットアップは2つの設計と1つのTclスクリプトを必要とするだけで、とても簡単です。

SLEC Tcl スクリプトは設計ファイル、インターフェース・マッピング、リセット条件、それにレイテンシ／スループットの値を確認します。SLEC は豊富な Tcl コマンド・セットを含み、これによってユーザはシーケンシャル・コンストレイント、階層構造をベースにしたブラックボックス、そして中間マッピング・ポイントを使って、高度なセットアップを作成することができます。

## 高度なデバッグ

SLEC は、2つのデザインが同じであると証明するか、または数サイクル（通常 10 入力処理以内）内の設計差を例証する短くて簡潔な反例を生成します。

設計のバグを再生させるために数千あるいは数百万のサイクルを必要とするかもしれないシミュレーションに比べ、SLECを使うと設計のデバッグが速くて、効率的です。反例はユーザが日常使用しているシミュレーション環境かデバッグ環境で見ることができ

る波形またはシミュレーション・テストベンチとして表現されます。

さらにユーザを補助するために、SLECが最初に発見した機能の差異ポイントを信号値と時間で表示します。

システム要件と互換性

- 言語：

VHDL 87/93、Verilog 95/2001

- シミュレータ：

ModelSim™、VCS®、NCSim™

- デバッガ：

Verdi™、SignalScan™

- オペレーティングシステム：

Redhat Enterprise Linux 3.0/4.0

- プラットフォーム：

32/64ビット x86 互換ハードウェア

- メモリ：

2GB 以上